地球上で最大の創業者である TSMC とサムスンは、すでに次世代の iPhone と Android スマートフォン チップの開発に取り組んでいます。 3 nm への移行により、最終的には 2 nm になります。コンポーネントのエネルギー消費をさらに大幅に削減しながら、コンポーネントをさらに強力にするのに十分な量です。

初めて一般の人も購入できるようになりましたiPhone 12は5nmチップを搭載。モバイル業界では彫刻の細かさが不可欠です。消費電力を大幅に削減しながら、より多くのトランジスタをより小さなスペースに収めることができます。。ただし、多くのブランドと同様に、Apple には独自のファウンドリがありません。

したがって、何世代にもわたってこの分野のリーダー、特にTSMCに呼びかけています。新しい A14 Bionic チップには 118 億個のトランジスタが組み込まれていますiPhone 11 の 85 億個の A13 Bionic チップに対して、もちろん、Apple だけが 5nm に取り組んでいるわけではないと反論することもできます。Huawei は新しいチップを発表したばかりです。Mate 40およびMate 40 Pro、同じく5nmで刻印された新しいKirin 9000チップを搭載さらに多くのトランジスタが搭載されています。しかしファーウェイの場合、米国の制裁により状況は複雑になる。

5nm以降のチップを焼くための必須機器にアクセスできる創業者はほんの一握りです

TSMC と競合するファウンドリはメーカーに供給できなくなりましたそれ以降のコンポーネントでは米国の新たな制裁が発効しました。これらの制裁米国の知的財産を使用する企業がファーウェイに部品を供給することを禁止する商務省から事前の承認を得ることなく。 TSMCがHuaweiに対して取得した認可ではありません。その結果、中国のメーカーが注文した1,500万個のKirin 9000チップのうち、実際に配送できるのは800万個だけ。

これにより、ファーウェイの売上は短期および中期的に大幅に制限されるはずだ。特にファーウェイにはそれがなかったので、Mate 40 でのみ Kirin 9000 を使用する予定– 5G ネットワーク ソリューションだけでなく、息子のスマホしなやかMate X2。来年 5nm クラブに参加すると予想される選手は他に 1 人だけです。 サムスン、次期Exynosチップを搭載そしてクアルコムのために刻むべきSnapdragon 875。または、サムスンとTSMCはすでにオランダの機器メーカーASMLと3nmおよび2nmの彫刻に取り組んでいます。。

彫刻の精緻さの向上と、より効率的なチップを提供するための ASML のような機器メーカーの中心的な役割。ちなみに、ファーウェイは貿易戦争が始まって以来、高性能チップの供給が途絶えるのを避けるために代替品を探してきた。中国には国家創設者である SMIC がいますが、その彫刻プロセスは依然として競合他社より遅れています (14 nm、まもなく 7 nm)。

基本的な限界に達するにつれてイノベーションは増大する

これはまさに、ASML のような機器メーカーがこれらのプレーヤーに最先端のマシンを供給する権利を失っているためです。彫刻の細かさを減らすほど、特に奇妙な効果が現れるため、技術的に可能な限界がさらに押し広げられます。したがって、一定の彫刻精度を維持し、電流漏れや一定のしきい値を超えると引き継ぐ外乱の影響を回避するには、これまで以上に洗練されたチップを採用する必要があります。。 5 nm の場合、Extreme UV (EUV) リソグラフィ プロセスを開発する必要がありました。

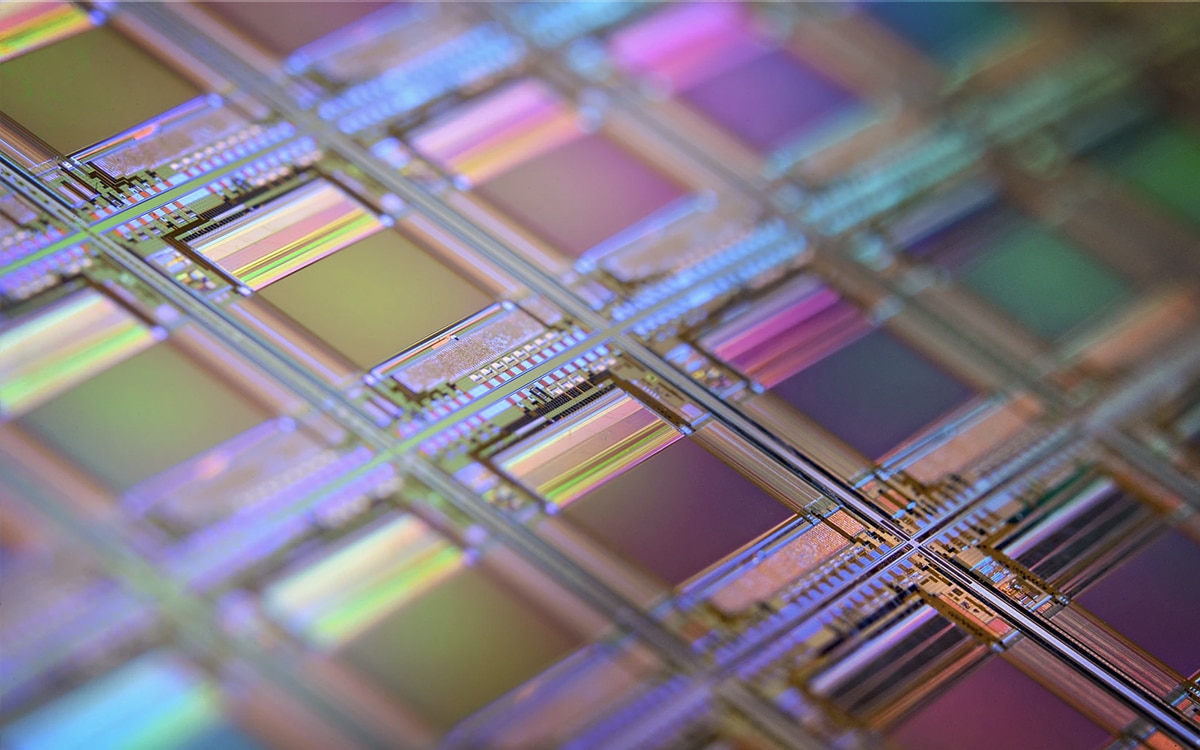

シリコン ウェーハ上ではさまざまな層が特に短い波長でエッチングされることを理解してください。ザトランジスタゲートの設計も適応されていますこのスケールで引き継ぐ量子効果を避けるためです(原子数個分の幅しかない元素について話しています)。ただし、これまで以上にパフォーマンスを向上させるには、TSMC、ASML、およびサムスンのような他のファウンドリも、各ダイ上のコンポーネント層の数を増やすことに関心を持っています。。

これらのレイヤーにより、より複雑なコンポーネントを作成できるようになります。これは、これらの規模では不可欠です。チップの設計はより複雑になります。それで今のところ、TSMC は現在、同じコンポーネント上に最大 14 層のエッチングを可能にする 5nm プロセスを使用しています。。 3 nm への移行だけでも、同じレベルの複雑さとトランジスタ数で、電力が 15% 増加し、エネルギー消費が 30% 削減されました。。

しかし、さらに優れたものを実現することは間違いなく可能です。ASML は、次のことを可能にするテクノロジーを開発しています。3 nm で同じダイ上に最大 20 層を焼きます。この進歩は、スマートフォン用 SoC と DRAM メモリ チップの両方に利益をもたらすはずです。 3 nm では、TSMC はいわゆる FinFET トランジスタ設計を選択します。これらは実際には 2 つのゲートを持つトランジスタです。 FinFET という名前は、ダイの表面に一種のラメラを形成するコンポーネントの特定の領域の形状に由来しています。これにより、部品の密度を高めながら周波数を高めることが可能になります。

2nmへの移行に向けて、TSMCはトランジスタの設計をさらに変更し、GAAFETテクノロジーに切り替える予定です(ゲートオールアラウンド)3nmを超えるMBCFET技術と並行してSamsungによって開発されました。シリコンエッチングの根本的な限界に近づくにつれて、今後数年間でエキサイティングな革新が見られるはずです。おそらく代替品が見つかるのを待っている間。

ソース :フォンアリーナ