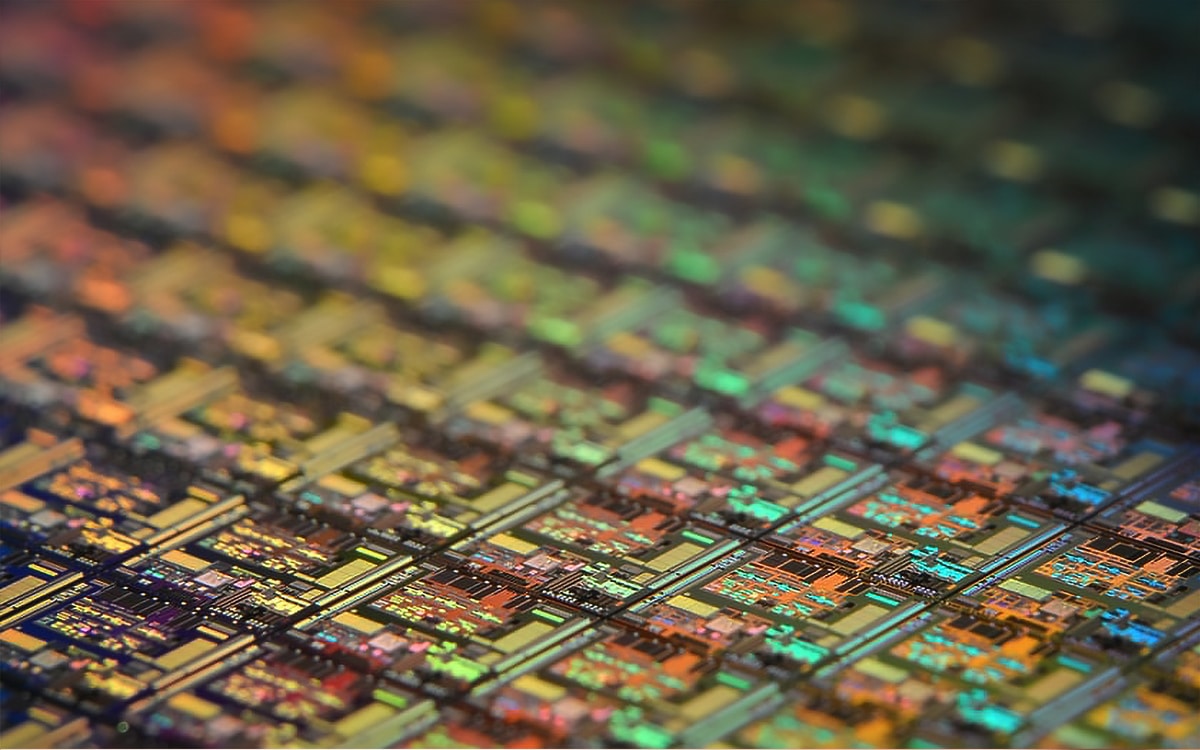

TSMCは年次報告書の中で、創業者が2019年からスマートフォンチップを2nmで刻印する準備をしていたことを明らかにした。同社はさらに微細な部品を彫刻するための予備研究も開始した。

TSMCは今月、5nmチップの量産を開始した。そして最新ニュース私たちは次のステップ – 3 nm – 2022 年までに待っています。しかし、創業者が株主向けに発行した年次報告書から、2nm彫刻に取り組む取り組みが実際には2019年にすでに始まっていることが分かりました。そして、さらに低い彫刻フィネスに関する予備研究がすでに始まっていることが分かりました。

現在、最高の SoC は 7nm で刻印されています。最初5nmで刻印されたチップセットは年末までに到着するはずだ– Appleはおそらくボールをオープンするだろう新しい A14 SoC を搭載。したがって、次のステップは3nm彫刻当初の予定より到着が1年前倒しされましたが、その後2025年までに2nm彫刻、創設者がその間にスケジュールを早めることができなかった場合。

7nm 彫刻と比較して、2nm 彫刻では 3.5 倍多くのトランジスタを同じ表面に配置できます。トランジスタの量を高密度化することは、モバイル業界にとって非常に重要です。これにより、省スペースでより多くのコンピューティング能力を提供できるだけでなく、チップのエネルギーへの影響を軽減してスマートフォンの自律性を拡張できるためです。

こちらもお読みください:EUは、ヨーロッパの-6nmプロセッサRISC-Vの製造にTSMCを選択しました…これが私たちが知っていることです

TSMC が回避しなければならない問題は、この規模では材料の物理的特性が変化することです。小型化が進むにつれて、これらの小さなシリコン ダイもより複雑になります。

ソース :フォンアリーナ